About Course

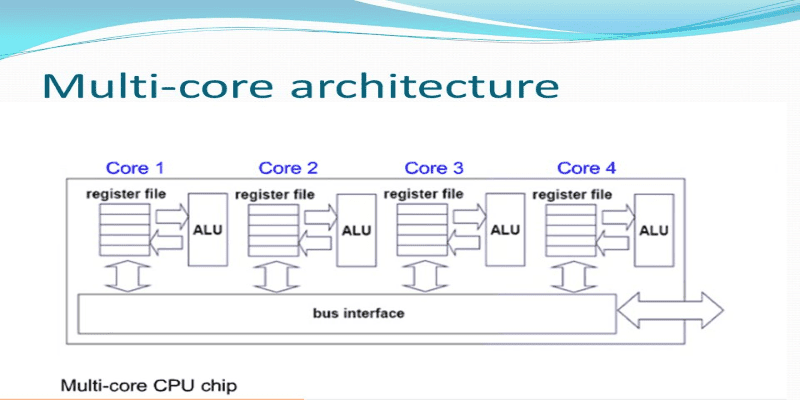

Multi-Core Computer Architecture – Storage and Interconnects. We are in the era of multi-core systems where even the simplest of handheld devices like a smartphone houses many processors in a single chip.

Multi-Core Computer Architecture. The core counts are ever-increasing from 8 to 10 in smartphones to over 100s in supercomputers. This course will introduce the students to the world of multi-core computer architectures. With the unprecedented growth of data science, on-chip storage systems and inter-core communication frameworks are getting equal attention as that of processors. This course will focus on delivering an in-depth exposure in memory-subsystems and interconnects of Tiled Chip Multi-Core Processors with few introductory sessions on advanced superscalar processors. The course concludes with pointers to current research standings and on-going research directions for motivating the students to explore further

COURSE LAYOUT

Week 1: Fundamentals of instruction pipeline for superscalar processor design

Week 2: Memory hierarchy design, cache memory – fundamentals and basic optimizations

Week 3: Cache memory – advanced optimizations, performance improvement techniques

Week 4: gem5 simulator – build and run, address translations using TLB and page table

Week 5: DRAM – organization, access techniques, scheduling algorithms, and signal systems.

Week 6: Introduction – Tiled Chip Multicore Processors (TCMP), Network on Chips (NoC)

Week 7: NoC router – architecture, design, routing algorithms, and flow control techniques.

Week 8: Advanced topics in NoC and storage – compression, prefetching, QoS.

Course Content

Multi-Core Computer Architecture – Storage and Interconnects

-

Multi-Core Computer Architecture – Storage and Interconnects [Introduction Video]

00:00 -

DRAM Controllers & Address Mapping

00:00 -

Address Translation Mechanisms

00:00 -

Main Memory Concepts

00:00 -

Introduction to Tiled Chip Multicore Processors

00:00 -

Routing Techniques in Network On Chip

00:00 -

Network On Chip Router Micro-Architecture

00:00 -

gem5 Simulator – NoC Optimisation

00:00 -

Energy Efficient Bufferless NoC Routers

00:00 -

Sidebuffered Deflection Routers

00:00 -

Concepts in Network on Chip

00:00 -

QoS of NoC and Caches in TCMP Systems

00:00 -

Emerging Trends in Network On Chips

00:00 -

Concepts in TCMP Systems

00:00 -

Introduction to DRAM System

00:00 -

Cache Memory Optimizations

00:00 -

Advanced Cache Optimization Techniques-II

00:00 -

Introduction and Overview of the Course

00:00 -

Instruction Execution Principles

00:00 -

Introduction to Instruction Pipeline

00:00 -

Introduction to Superscalar Pipelines

00:00 -

Instruction Pipeline & Performance – I

00:00 -

Instruction Pipeline & Performance – II

00:00 -

Introduction to Cache Memory

00:00 -

Block Replacement Techniques & Write Strategy

00:00 -

gem5 Simulator – An Overview

00:00 -

Cache Memory

00:00 -

Basic Cache Optimization Techniques

00:00 -

gem5 Simulator – Cache Optimisation

00:00 -

Advanced Cache Optimization Techniques-I

40:09 -

Multiprocessor Computer Architecture: Why, How and What’s next ?

00:00

Student Ratings & Reviews